# DDR 布板注意事项

---

文件标识：RK-SM-YF-036

发布版本：V1.3.1

日期：2021-02-25

文件密级：绝密 秘密 内部资料 公开

## 免责声明

本文档按“现状”提供，瑞芯微电子股份有限公司（“本公司”，下同）不对本文档的任何陈述、信息和内容的准确性、可靠性、完整性、适销性、特定目的性和非侵权性提供任何明示或暗示的声明或保证。本文档仅作为使用指导的参考。

由于产品版本升级或其他原因，本文档将可能在未经任何通知的情况下，不定期进行更新或修改。

## 商标声明

“Rockchip”、“瑞芯微”、“瑞芯”均为本公司的注册商标，归本公司所有。

本文档可能提及的其他所有注册商标或商标，由其各自拥有者所有。

版权所有 © 2021 瑞芯微电子股份有限公司

超越合理使用范畴，非经本公司书面许可，任何单位和个人不得擅自摘抄、复制本文档内容的部分或全部，并不得以任何形式传播。

瑞芯微电子股份有限公司

Rockchip Electronics Co., Ltd.

地址：福建省福州市铜盘路软件园A区18号

网址：[www.rock-chips.com](http://www.rock-chips.com)

客户服务电话：+86-4007-700-590

客户服务传真：+86-591-83951833

客户服务邮箱：[fae@rock-chips.com](mailto:fae@rock-chips.com)

## 前言

### 概述

记录所有平台的 DDR 布板注意事项

### 产品版本

| 芯片名称 | 内核版本   |

|------|--------|

| 所有芯片 | 所有内核版本 |

### 读者对象

本文档（本指南）主要适用于以下工程师：

硬件工程师

### 修订记录

| 版本号    | 作者  | 修改日期       | 修改说明                           |

|--------|-----|------------|--------------------------------|

| V1.0.0 | 何灿阳 | 2017-11-02 | 初始版本                           |

| V1.1.0 | 陈炜  | 2017-11-09 | 更改某些表述                         |

| V1.2.0 | 汤云平 | 2018-01-14 | 增加 RK3326 描述及 LPDDR2/LPDDR3 要求 |

| V1.3.0 | 陈有敏 | 2018-10-08 | 增加总容量 3GB 说明和 RK3399 单通道布线要求   |

| V1.3.1 | 黄莹  | 2021-02-25 | 修改格式                           |

## 目录

### DDR 布板注意事项

1. 名词说明

2. 总的要求

3. RK3399 特殊要求

4. RK3326、PX30 特殊要求

# 1. 名词说明

- **颗粒**: 指各种 DDR memory, DDR3 memory、DDR4 memory、LPDDR3 memory、LPDDR4 memory、LPDDR2 memory

- **CS**: 主控或 DDR memory 的片选信号

- **rank**: 就是 CS, 就是片选信号

- **byte**: 主控每 8 根 DDR 信号线, 成为一个 byte。所以 byte0 指 DQ0-DQ7, byte1 指 DQ8-DQ15, byte2 指 DQ16-DQ23, byte3 指 DQ24-DQ31。注意, 这里的 DQ 都是说主控的, 颗粒的 DQ 不一定跟主控的 DQ 是一一对应连接的。

- **bank**: 是指 DDR memory 的 bank 数量

- **column**: 是指 DDR memory 的 column 数量

- **row**: 是指 DDR memory 的 row 数量

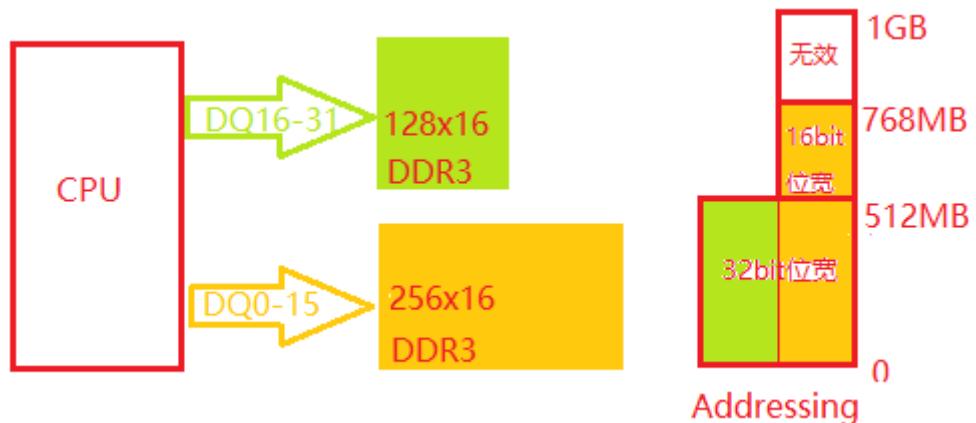

- **AXI SPLIT**: 非对称容量组合模式, 如高位寻址区为 16bit 位宽, 低位寻址区为 32bit 位宽。例如常规的组合为 256x16+256x16, 而 AXI SPLIT 的组合为 256x16+128x16=768MB, 在高位寻址区只剩 16bit 位宽, 示意图如下图。

# 2. 总的要求

总的要求适用于所有平台, 各款主控的特殊要求, 后面单独列出

- 1、**DQ** 的交换, 不能超出该组 **byte**, 只能在 **byte** 内部进行交换。有些主控有特殊要求, **byte** 内部都不能交换, 见具体主控的特殊要求

- 2、用到 2 个 CS 上的 **bank**、**column** 数量不同的 **DDR** 颗粒, 需要跟软件确认是否支持

- 3、如果颗粒只有一个 CS, 只能接在主控的 **CS0** 上

- 4、如果只用一个通道, 只支持通道 **0**

- 5、如果颗粒 2 个 CS 的容量不同, 则容量小的应该放在主控的 **CS1** 上

- 6、所有平台, 不支持大于 2 个 CS 的颗粒

- 7、如果颗粒只有一个 **ODT** (像 LPDDR3), 应该连到 **ODT0** 上

## 8、6Gb、12Gb 的使用比较特殊（8Gb、4Gb、2Gb 没有这条限制）

目前只支持一个通道上的 2 个 CS 都是 6Gb 或者 2 个 CS 都是 12Gb 的，不支持 6Gb、12Gb 与 8Gb、4Gb、2Gb 混合在 2 个 CS 中使用。

比如：

| CS0  | CS1  | 支持情况                        |

|------|------|-----------------------------|

| 6Gb  | 6Gb  | 支持                          |

| 12Gb | 12Gb | 支持                          |

| 6Gb  | 12Gb | 不支持 违反要求 5，并且这样组合也不支持       |

| 12Gb | 6Gb  | 不支持，这种组合也不支持                |

| 8Gb  | 6Gb  | 不支持 8Gb 和 6Gb 混合在 2 个 CS 中  |

| 12Gb | 8Gb  | 不支持 12Gb 和 8Gb 混合在 2 个 CS 中 |

| 6Gb  | 4Gb  | 不支持 6Gb 和 4Gb 混合在 2 个 CS 中  |

| 12Gb | 4Gb  | 不支持 12Gb 和 4Gb 混合在 2 个 CS 中 |

## 9、颗粒的 RZQ 不能共用

### 10、DDR4 目前连接方式暂无特殊要求

### 11、外接 LPDDR2 或 LPDDR3 时，DDR0 的 DQ0-DQ7 应该一一对应的连接到 DRAM 的 DQ0-DQ7

### 12、双通道 DRAM 总容量 3GB 支持情况

双通道 DRAM 总容量 3GB 支持的颗粒组合如下图：

|             |   |      | LPDDR3 X16(2die)  |     |     |     | LPDDR3 X32(1die) |     |     |     | DDR3 X16(2die) |     |     |     |

|-------------|---|------|-------------------|-----|-----|-----|------------------|-----|-----|-----|----------------|-----|-----|-----|

|             |   |      | cs0               |     | cs1 |     | cs0              |     | cs1 |     | cs0            |     | cs1 |     |

|             |   |      | col               | row | col | row | col              | row | col | row | col            | row | col | row |

| 1.5GB+1.5GB | 1 | cha: | 6Gb/cs0 + 6Gb/cs1 |     |     |     |                  | 10  | 15  | 10  | 15             |     |     |     |

|             |   | chb: | 6Gb/cs0 + 6Gb/cs1 |     |     |     |                  | 10  | 15  | 10  | 15             |     |     |     |

|             | 2 | cha: | 12Gb/cs0          | 11  | 15  |     |                  | 11  | 15  |     |                |     |     |     |

|             |   | chb: | 12Gb/cs0          | 11  | 15  |     |                  | 11  | 15  |     |                |     |     |     |

|             | 3 | cha: | 8Gb/cs0 + 4Gb/cs1 |     |     |     |                  | 10  | 15  | 10  | 14             | 10  | 15  | 10  |

|             |   | chb: | 8Gb/cs0 + 4Gb/cs1 |     |     |     |                  | 10  | 15  | 10  | 14             | 10  | 15  | 10  |

|             | 4 | cha: | 16Gb/cs0          | 11  | 15  |     |                  | 11  | 15  |     |                | 10  | 16  |     |

|             |   | chb: | 8Gb/cs0           | 11  | 14  |     |                  | 10  | 15  |     |                | 10  | 15  |     |

|             | 5 | cha: | 16Gb/cs0          |     |     |     |                  | 11  | 15  |     |                | 10  | 16  |     |

|             |   | chb: | 4Gb/cs0 + 4Gb/cs1 |     |     |     |                  | 10  | 14  | 10  | 14             | 10  | 14  | 10  |

|             | 6 | cha: | 8Gb/cs0 + 8Gb/cs1 | 11  | 14  | 11  | 14               | 10  | 15  | 10  | 15             | 10  | 15  | 10  |

|             |   | chb: | 8Gb/cs0           | 11  | 14  |     |                  | 10  | 15  |     |                | 10  | 15  |     |

|             | 7 | cha: | 8Gb/cs0 + 8Gb/cs1 |     |     |     |                  | 10  | 15  | 10  | 15             | 10  | 15  | 10  |

|             |   | chb: | 4Gb/cs0 + 4Gb/cs1 |     |     |     |                  | 10  | 14  | 10  | 14             | 10  | 14  | 10  |

说明：1) RK3288, RK3399 支持双通道。

### 13、单通道 DRAM 总容量 3GB 支持情况

单通道 DRAM 总容量 3GB 支持的颗粒组合如下图：

|   | LPDDR3              |           |           |           | LPDDR3    |           |           |           | LPDDR3 |     |     |     | LPDDR3 |     |     |     |

|---|---------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--------|-----|-----|-----|--------|-----|-----|-----|

|   | cs0                 |           | cs1       |           | cs0       |           | cs1       |           | cs0    |     | cs1 |     | cs0    |     | cs1 |     |

|   | X32(1die)           | X32(1die) | X16(2die) | X16(2die) | X32(1die) | X16(2die) | X16(2die) | X32(1die) | col    | row | col | row | col    | row | col | row |

| 1 | 24Gb/cs0            |           |           |           | 12        | 15        |           |           |        |     |     |     |        |     |     |     |

| 2 | 12Gb/cs0 + 12Gb/cs1 | 11        | 15        | 11        | 15        | 11        | 15        | 11        | 15     | 11  | 15  | 11  | 15     | 11  | 15  | 11  |

| 3 | 16Gb/cs0 + 8Gb/cs1  |           |           |           | 11        | 15        | 11        | 14        | 11     | 15  | 11  | 14  |        |     |     |     |

|   | DDR3                |           |          |          | DDR3      |          |          |           | DDR3 |     |     |     | DDR3 |     |     |     |

|---|---------------------|-----------|----------|----------|-----------|----------|----------|-----------|------|-----|-----|-----|------|-----|-----|-----|

|   | cs0                 |           | cs1      |          | cs0       |          | cs1      |           | cs0  |     | cs1 |     | cs0  |     | cs1 |     |

|   | X16(2die)           | X16(2die) | X8(4die) | X8(4die) | X16(2die) | X8(4die) | X8(4die) | X16(2die) | col  | row | col | row | col  | row | col | row |

| 1 | 24Gb/cs0            |           |          |          |           |          |          |           |      |     |     |     |      |     |     |     |

| 2 | 12Gb/cs0 + 12Gb/cs1 |           |          |          |           |          |          |           |      |     |     |     |      |     |     |     |

| 3 | 16Gb/cs0 + 8Gb/cs1  | 10        | 16       | 10       | 15        | 10       | 16       | 10        | 15   | 10  | 16  | 10  | 15   | 10  | 16  | 10  |

### 3. RK3399 特殊要求

- 1、CS2 是 CS0 的复制信号，CS3 是 CS1 的复制信号，其行为与被复制信号完全一样

- 2、CLK 走线必须比该通道任意一组 DQS 都长，ddr PHY 的要求

- 3、LPDDR3 的 D0-D15 必须和主控完全一一对应的连接

- 4、LPDDR3 的 D16、D24 这 2 根数据线也必须和主控完全一一对应连接

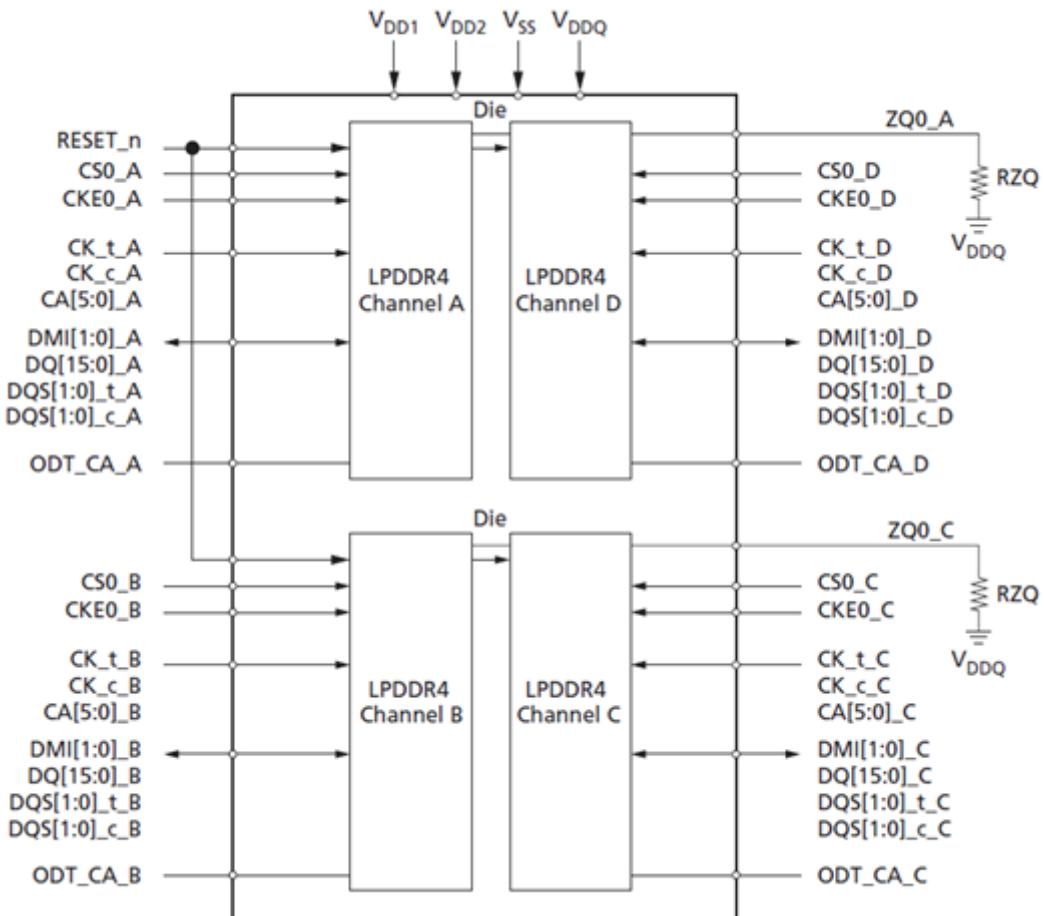

- 5、注意主控一个通道与 LPDDR4 颗粒 2 个通道的组成关系

采用颗粒的 Channel A + Channel C 组成一个 32bit，和 Channel B + Channel D 组成一个 32bit，这种方法，能做到避免 ZQ 共用的问题

6、LPDDR4 的 RZQ 要通过 240 电阻接 VDDQ，而不是 GND，这点要注意，RK3399 主控端没有变，还是一样 RZQ 通过 240 电阻接 GND

7、接 LPDDR4 时，主控端的 DDR0\_ODT0/1, DDR1\_ODT0/1 悬空，不用连到 LPDDR4 颗粒。而颗粒端的 ODT\_CA\_X 默认通过 10K 电阻上拉到 VDDQ，暂时预留 DNP 的下拉电阻

8、LPDDR4 所有数据线（DQ）都不能对调，不管组内，还是组间

9、如果只用 channel 0, channel 1 也需要供电

## 4. RK3326、PX30 特殊要求

---

### 1、支持的位宽组合方式

1. 32bit 最大位宽（大容量 16bit+小容量 16bit），举例： $256 \times 16 + 128 \times 16 = 768\text{MB}$ 。

2. 16bit 最大位宽（大容量 8bit+小容量 8bit），举例： $512 \times 8 + 256 \times 8 = 768\text{MB}$ 。

### 2、颗粒要求

AXI SPLIT 模式下，要求所有颗粒的 column, bank 是相同的。

### 3、连接要求

1. AXI SPLIT 模式下，要求在使用 16bit 位宽的颗粒时，需要将 AP DDR 控制器的 byte0/1 接在一个颗粒上，将 byte2/3 接在一个颗粒上。

2. AXI SPLIT 模式下，要求较大容量的颗粒连接到 AP DDR 控制器的低位区，如 byte0 或 byte0/1, 举例：16bit a 颗粒+16bit b 颗粒组成 32bit 位宽，如果 a 颗粒的容量大，则 a 颗粒连接到 byte0/1。

3. 如果使用 2 个 CS，则只有 CS1 支持 AXI SPLIT，允许两种方式：

1. CS1 上采用非对称容量，如 CS0 上为 32bit 总位宽，则 CS1 上采用大容量 16bit+小容量 16bit 颗粒拼接成 32bit，如 CS0 上为 16bit 总位宽，则 CS1 上采用大容量 8bit+小容量 8bit 颗粒拼接成 16bit。

2. CS1 上只贴一半位宽的颗粒，要求其 row $\leq$ CS0 上的颗粒。如 CS0 为 32bit 总位宽，则 CS1 贴 16bit 的颗粒，如 CS0 为 16bit 总位宽，则 CS1 贴 8bit 的颗粒。

4、下表列举出了所有支持的 AXI SPLIT 的容量组合。该表格之外的 AXI SPLIT 组合都不支持。

| NO. | CS0                              | CS1                                       | 支持情况 |

|-----|----------------------------------|-------------------------------------------|------|

| 1   | 16bit 最大位宽 (大容量 8bit+小容量 8bit)   | 无颗粒                                       | 支持   |

| 2   | 32bit 最大位宽 (大容量 16bit+小容量 16bit) | 无颗粒                                       | 支持   |

| 3   | 32bit 固定位宽                       | 32bit 最大位宽 (大容量 16bit+小容量 16bit)          | 支持   |

| 4   | 32bit 固定位宽                       | 16bit 固定位宽, 接 Byte0/1 (row<=cs0 上的颗粒 row) | 支持   |

| 5   | 16bit 固定位宽                       | 16bit 最大位宽 (大容量 8bit+小容量 8bit)            | 支持   |

| 6   | 16bit 固定位宽                       | 8bit 固定位宽, 接 Byte0 (row<=cs0 上的颗粒 row)    | 支持   |

5、常规应用同其他平台一致。